2024年3月14日,由达摩院主办的第二届玄铁RISC-V生态大会在深圳圆满举行。大会以“开放·连接”为主题,聚焦了RISC-V技术在各行业中的商业化成功案例及其最新研发成果。思尔芯,作为国内首家数字EDA供应商,不仅应邀参与此次盛会,还在会场设立了展台,向参会者展示了针对RISC-V开发的全面的数字前端解决方案,赋能芯片设计。

面对RISC-V技术日益渗透各行业的趋势,尽管其开源、简洁和高度可扩展的特点受到广泛赞誉,但其生态系统的完善仍面临挑战,尤其是系统碎片化问题。为此,思尔芯通过“芯神匠”的系统和应用性能分析、“芯神瞳”的评估架构配置和软件性能分析、“芯神鼎”的规范符合性测试等策略,致力于构建一个更高效、更稳定的RISC-V平台。

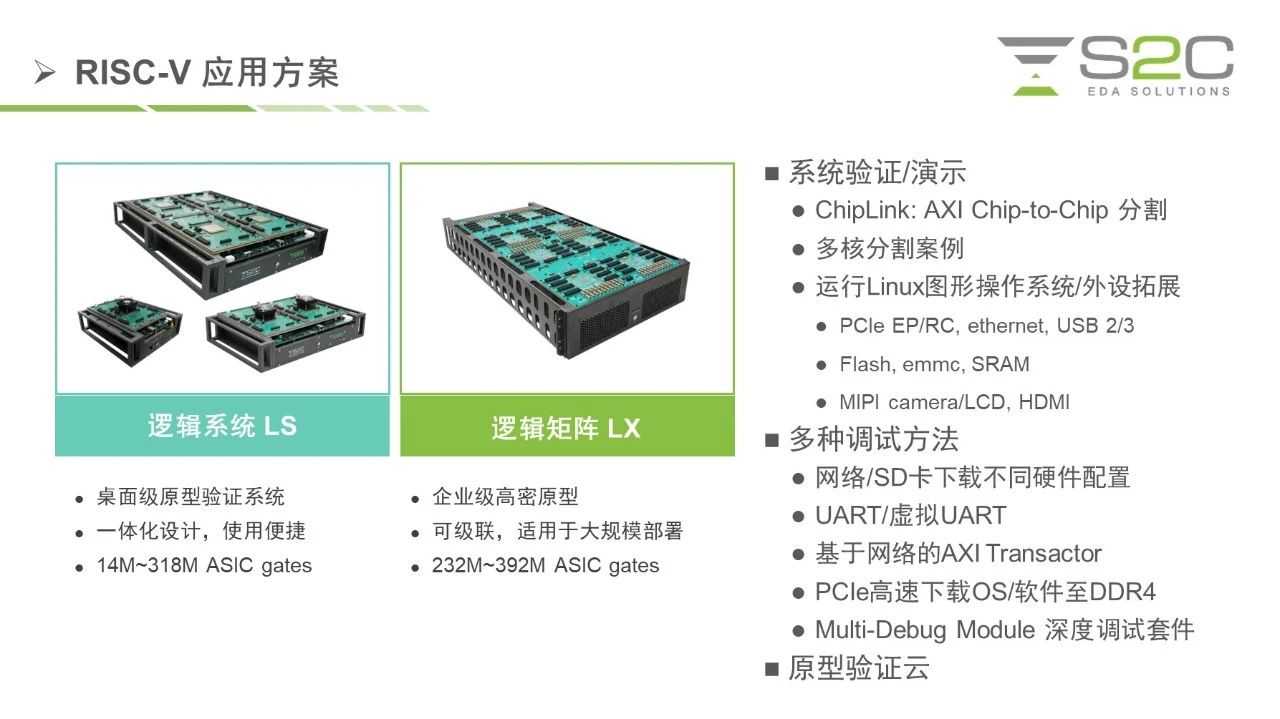

大会现场,思尔芯Prodigy芯神瞳原型验证解决方案如何助力RISC-V开发受到关注。这套解决方案在面对高度碎片化的RISC-V市场应用时,提供了一系列关键功能,如系统验证与演示、多种调试方法,以及原型验证云服务等,这些都极大地支持了RISC-V的开发和应用。

针对RISC-V架构的开放和模块化特性,思尔芯的AXI Chip to Chip IP优化了数据传输流程,提高了多核AXI-based SoC的数据处理能力,这对执行复杂计算和处理大量数据的RISC-V应用至关重要。此外,随着RISC-V越来越依赖于处理高性能计算任务的能力,思尔芯的Chiplink AXI IP方案支持高达1024位宽的AXI DATA位宽,并能在每个Bank支持最多4组AXI协议,同时提供多种可配置的Serdes线速率,显著提升了多核处理器和AXI周边设备的速度和性能。

拥抱开源,与世界协同创新。中国工程院院士倪光南院士在大会上强调了RISC-V在国际上成为重要力量的期望,并呼吁大家协同创新,共同为RISC-V生态的发展贡献力量。思尔芯所展示的针对RISC-V创新技术和解决方案,这些创新对于满足日益增长的RISC-V应用性能要求至关重要,并推动了RISC-V生态系统的成熟与发展。

欲了解思尔芯更多信息,请点击:https://www.s2ceda.com