PegaSim芯神驰是思尔芯倾力打造的一款高性能、多语言混合的商用数字逻辑仿真器。PegaSim采用了创新的架构算法,实现了高性能的仿真引擎和约束求解器引擎,支持多种设计与验证语言,包括SystemVerilog、Verilog、VHDL和UVM验证方法学等。

支持IEEE1800-2017SystemVerilog,IEEE1364Verilog和IEEE1076-1993VHDL

支持UVM,VMM和OVM方法学

支持时序反标(SDF&Timing check)

完整的混合仿真DPI与VPI支持

支持自动增量和并行设计编译技术

可媲美业内领先商用仿真器的编译效率与运行性能

芯片验证过程中,可以通过分析RTL 代码的覆盖率来衡量验证的完备性。PegaSim集成了覆盖率分析工具,以支持覆盖率驱动的验证方法,帮助定义、度量和报告代码覆盖率目标,并发现覆盖率漏洞。

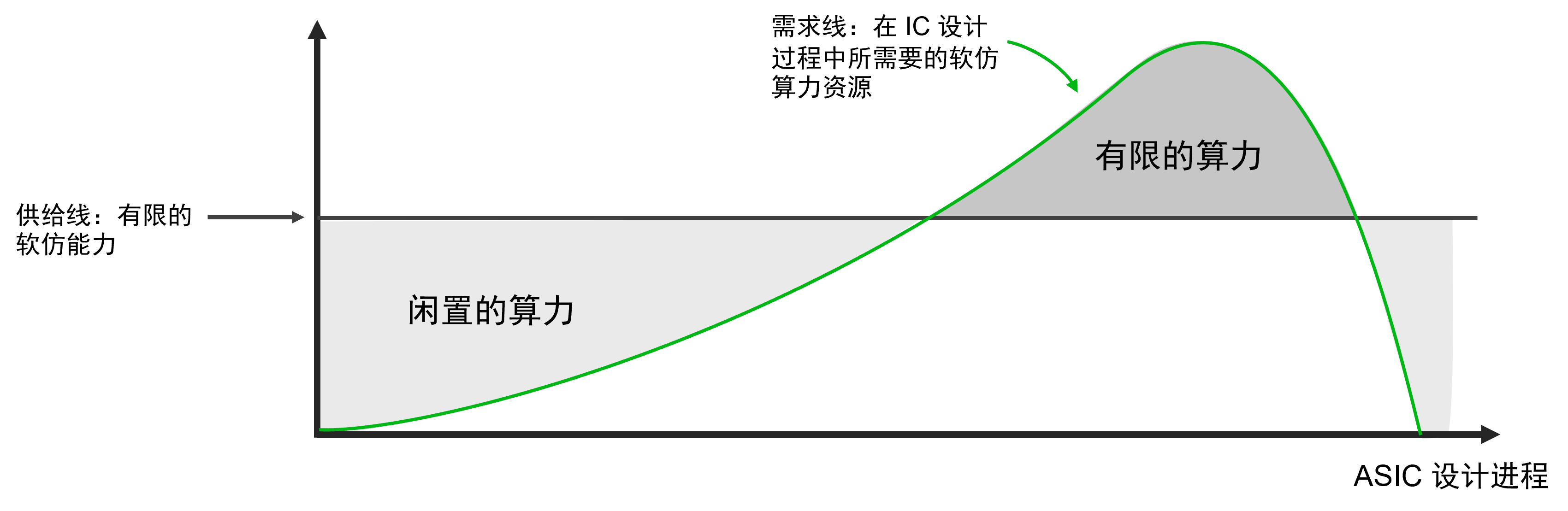

在一个芯片的开发流程中,设计工程师会应用硬件描述语言(HDL)来设计数字电路。为了保证芯片功能的正确性,在数字电路的仿真中,软件仿真会通过计算机给出的各种测试激励来模拟芯片在真实环境下的运行状况。在搭建的测试环境中,软件仿真会编译这些代码,并计算出仿真结果。验证是一个不断迭代的过程,需要不断编写或修改测试来覆盖功能点和RTL代码。在仿真过程中,不断发现问题,更正问题,回归测试……循环往复的同时,不断进行功能覆盖率、代码覆盖率分析,使覆盖率趋于收敛。这种基于软件的逻辑仿真在整个功能验证中都需要用到。虽然软件仿真技术对工程师来说非常有必要,但就现有的商业模式来说,软件仿真的仿真能力和算力都与软件许可证(software license)挂钩。供应商提供的商用软件仿真服务会以license的形式收费。但在实际使用时,工程师们难以依赖经验进行有效算力与工具需求计算的匹配。

因为项目开发中对于算力的需求是波动的。有时候已购买的license无法满足现实使用需求,有部分设计工程师获取不到就会造成抢占或拥堵。但如果超前部署,又会带来巨额的成本投入,有可能在闲置时造成资源的浪费。这就对芯片开发效率产生致命影响。对于企业来说怎么平衡生产和效益匹配的问题是当下急需解决的事情。

完全的并行计算

大规模弹性存储

随时随地都可用

安全性能有保障

无需IT维护成本

快速可靠地完成