Advanced RISC Machines (ARM)

Arm架构在当今科技领域中占据着至关重要的地位。Arm架构凭借出色的能源效率、灵活性和性能,已经稳居全平台主流架构之一,不仅在移动设备领域占据绝对地位,还在桌面计算、服务器领域以及云计算等高性能应用中发挥着

关键作用。Arm的生态系统丰富,与全球众多合作伙伴共同推动其发展,使其在科技行业中具有广泛的影响力。随着技术的不断进步和应用需求的不断增长,Arm架构将继续发挥其优势。

思尔芯的Arm相关解决方案

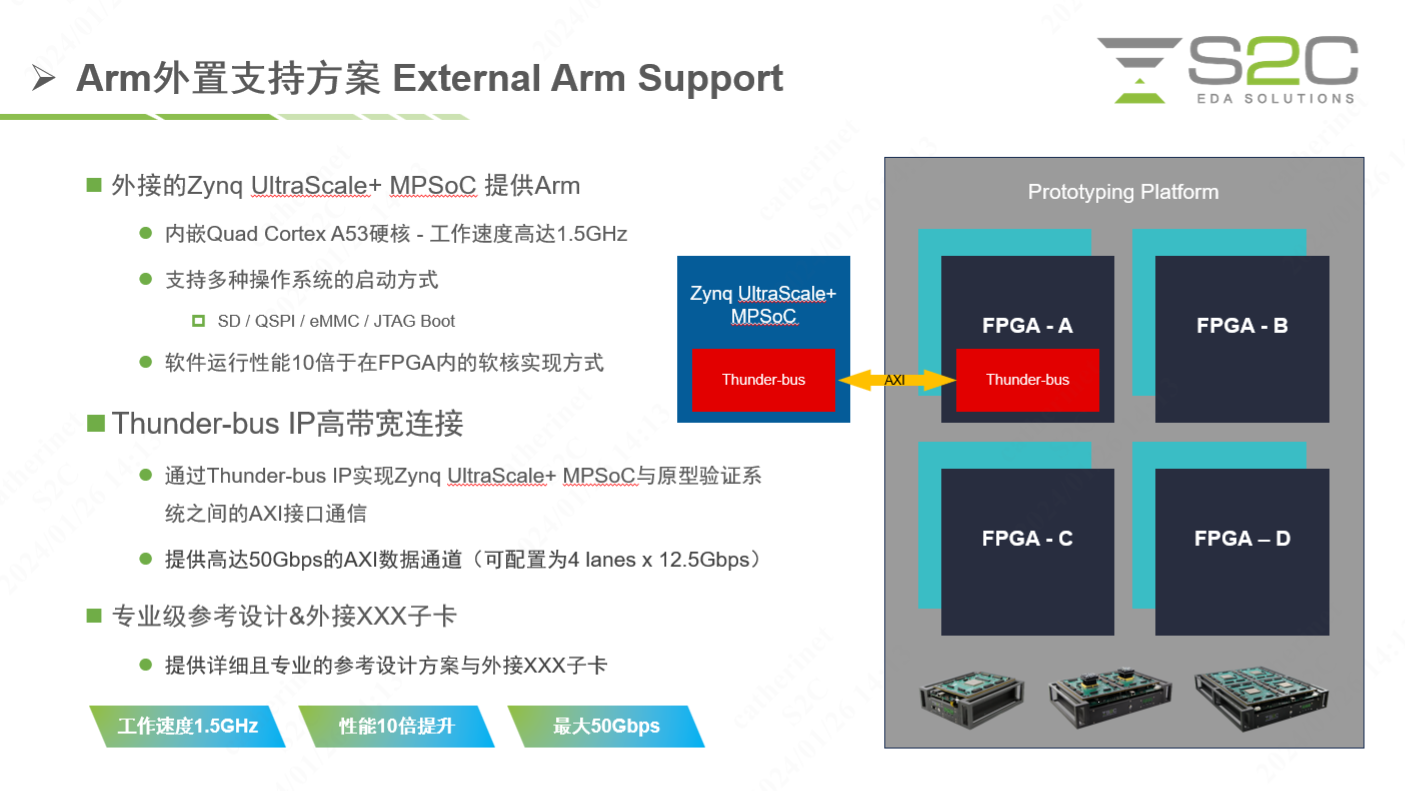

Arm外设IP的验证或是操作通常会搭配Arm CPU核的运行。通常用户会选择在Zynq UltraScale+ MPSoC内验证,因其FPGA集成了Arm 内核和 AXI 结构接口,是低门数容量验证的最佳选择。但是,对于规模较大的IP,受Zynq

UltraScale+ MPSoC可编程门数的限制,往往需要桥接一个更大容量的 FPGA。通过AMD-Xilinx Chip-to-Chip IP建立的片间连接,可以实现Zynq UltraScale+ MPSoC与原型验证系统之间的AXI接口通信,数据传输速率高达

50Gbps。思尔芯针对Zynq UltraScale+ MPSoC开发中常用的评估板——Xilinx ZC7(ZC702/ZC706/ZCU102)提供Prodigy Zynq接口模块,方便ZC7与芯神瞳原型验证系统或逻辑模块进行物理连接。

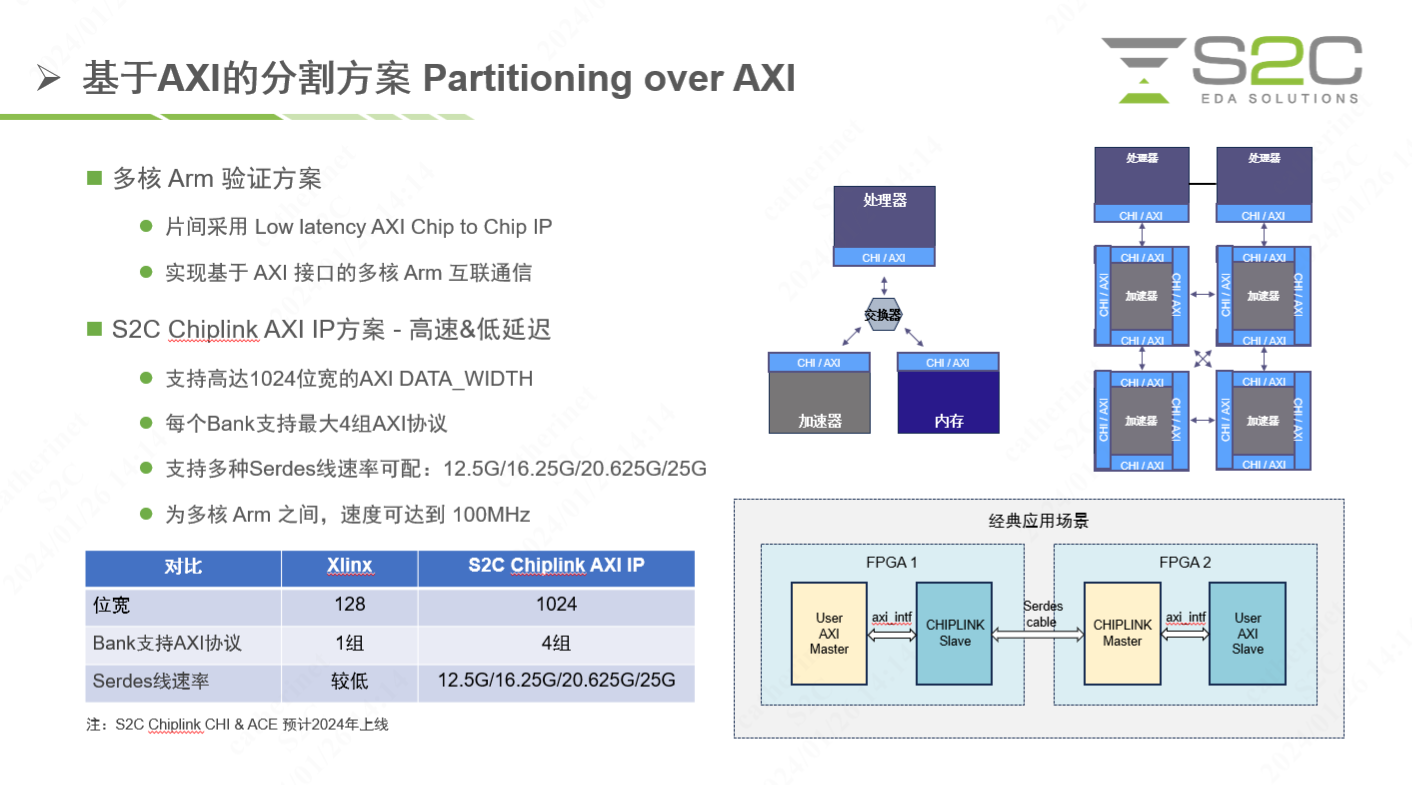

除了IP验证,在基于Arm的SoC设计中,Chip-to-Chip IP在基于AXI的多核分割时也具有重要作用。传统的TDM方法通常会降低系统运行速度(<= 25MHz),而基于 AXI 的Chip-to-Chip IP则在支持通过 AXI 进行多周期运行的同事

仍保持 50 MHz 以上的系统速度。针对在SoC分割上需要更强大的Chip-to-Chip功能,思尔芯推出自主研发的高速&低延迟AXI Chip-to-Chip IP 方案,Chiplink。Chiplink支持高达 1024 位的 AXI 总线宽度,每组最多可容纳4组

AXI 协议。它还支持多种 Serdes 线路速率(12.5G/16.25G/20.625G/25G)以供用户选择,使多核Arm之间数据传输速率达到100MHz,充分满足高性能计算的数据传输需求。

高带宽 AXI Transactor – ProtoBridge

思尔芯还配有高带宽 AXI Transactor — ProtoBridge AXI 协同仿真软件,该软件采用业内广泛使用的 AXI-4 总线协议以及独有的技术,通过PCIe在PC 主机和 原型验证平台之间建立4GB/s的高吞吐量数据通道, 使设计人员提升工作效率,从而缩短验证周期。

更多信息请联系我们