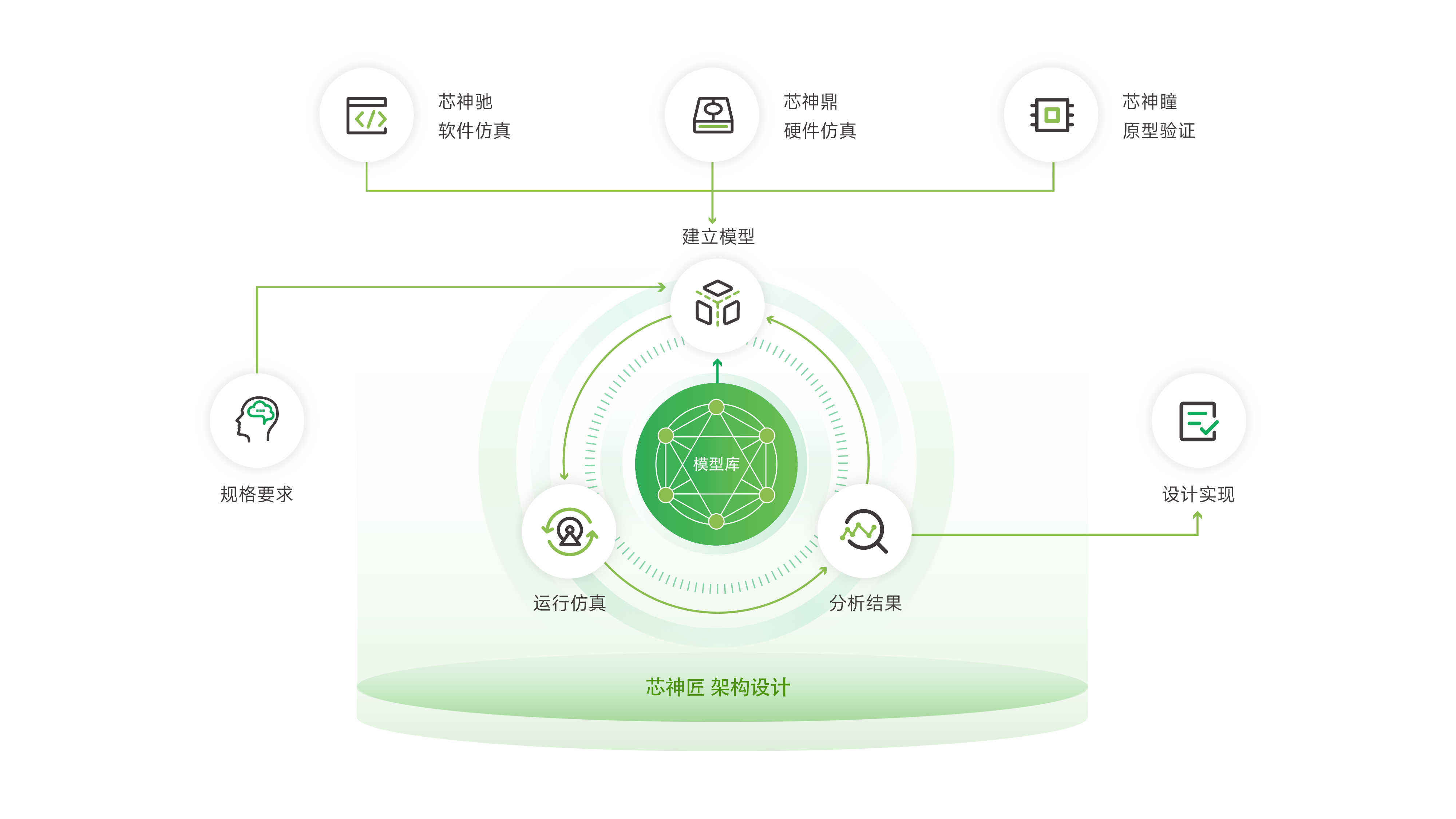

芯神匠架构设计软件提供了一个建模、分析、仿真和软硬件协作的平台,利用建模方法学实现电子系统级 (Electronic System Level,ESL) 设计流程,可用于开发半导体、航空和汽车电子系统设计产品。亦可基于 Arm、RISC-V 等平台下的早期软件开发验证及基于芯片性能分析的芯片架构探索。通过该方案创建周期精度的模型,以便进行早期性能和功耗分析, 也可进行时序和功耗的仿真,还能搭配我们的“芯神驰软件仿真”、“芯神鼎硬件仿真”、“芯神瞳原型验证” 产品, 提前进行软硬件协同设计。

多抽象层次建模仿真:

可选择不同的抽象层次,进行灵活的建模与仿真

支持IP、SoC、系统进行性能分析和功能验证

多种需求在一个平台上进行仿真,最大化模型复用率

可扩展的虚拟平台:

附带了大量的建模组件,用于开发完整的自定义组件/子系统

可与其他 EDA 工具互联,研究系统的性能、功能和信号的精准性

利用现有IP 进行快速且准确的混合仿真

支持通过 FPGA 进行仿真加速:

可搭配Prodigy 原型验证系统,加速部分组件仿真速率

解决设计师对建模的投入时间和建模学习的挑战,获得更佳的效率和精准度

支持与硬件仿真协同仿真:

通过硬件仿真搭建混合仿真系统,提高测试覆盖率、生产力和质量

支持运行真实业务软件进行DUT调试,在调试过程中可以主动暂停时钟,提供内部寄存器可视化等功能,提高测试效率和质量

电子系统级(ESL)架构设计流程