Reduced Instruction Set Computer-Five (RISC-V)

一、RISC-V:开源与自由度的完美结合

RISC-V是一种基于“精简指令集(RISC)”设计的开源指令集架构。相较于ARM和x86,RISC-V的架构更为精炼。具体而言,RISC-V的规范文档只有145页,而其“特权架构文档”更是只有91页,这无疑为硬件和软件开发带来更高的效率。当前RISC-V具有三大优势:

模块化设计:RISC-V采用模块化的组织结构,通过一套统一的指令集架构来满足各种不同的应用场景。这种模块化设计是x86和ARM架构所不具备的

指令数目少:RISC-V的指令集极为精炼,基础的RISC-V指令数目仅有40多条。即使加上各种模块化扩展,总指令数也相当有限,这样不仅提高了CPU的执行效率,还降低了功耗

开源与自由度:作为一个开源架构,RISC-V有全套开源免费的编译器、开发工具和软件开发环境(IDE)。这大大降低了门槛,使得任何人都可以对其进行定制和扩展

RISC-V以其开源和高度可定制的特性,正逐渐改变全球半导体市场的格局,给芯片设计和制造带来了前所未有的可能性。在全球政治经环境日趋复杂的今天,RISC-V为我国在半导体领域的自主可控和快速发展提供了一个难得的机会

RISC-V架构在物联网(IoT)、服务器和存储市场等多个领域拥有巨大的应用潜力。在物联网方面,其开源和高度可定制的特质赋予了它快速适应多元化市场需求的能力,对于个别物联网的应用都可以做个别的定制。虽然在服务器和高性能计算领域仍然处于初级阶段,RISC-V凭借其高成本效益和灵活可定制的特点,有很大机会突破这一市场。在数据存储方面,随着计算需求的增长,RISC-V的低功耗和高度定制性也呈现为有效的解决方案。尽管RISC-V在硬件方面具有多重优势,但要在非IoT等复杂的市场环境中取得更大的成功,还需加强其软件生态系统。与基于x86架构的Windows或基于ARM架构的Android相比,RISC-V目前还缺乏一个广泛认可的软件栈(software stack),这在高度碎片化的IoT领域尤为突出。主要挑战有:

碎片化与稳定性

兼容性问题:低成本的授权方式和厂商可以自定义指令的特点可能会影响到RISC-V标准的持续稳定性,以及软件和编译器生态系统的向后/向前兼容性

标准细节的挑战

漫长的演变过程:在服务器和移动设备方面,标准的细节定义存在很多需要解决的问题,这需要一个长期的演变和改进过程

EDA支持

成熟度问题:RISC-V的应用实例仍在不断成熟,对于稍大型的商用设计,通常需要大量修改RTL(寄存器传输级)代码

IP开发和适配:为了满足多样化的应用需求,还需要开发新的IP(知识产权)组件,并进行旧有经典IP的适配

RISC-V面临的不仅是硬件的挑战,更包括软件生态、标准化和成熟度等多方面的问题,这些都需要行业与社区的共同努力来解决

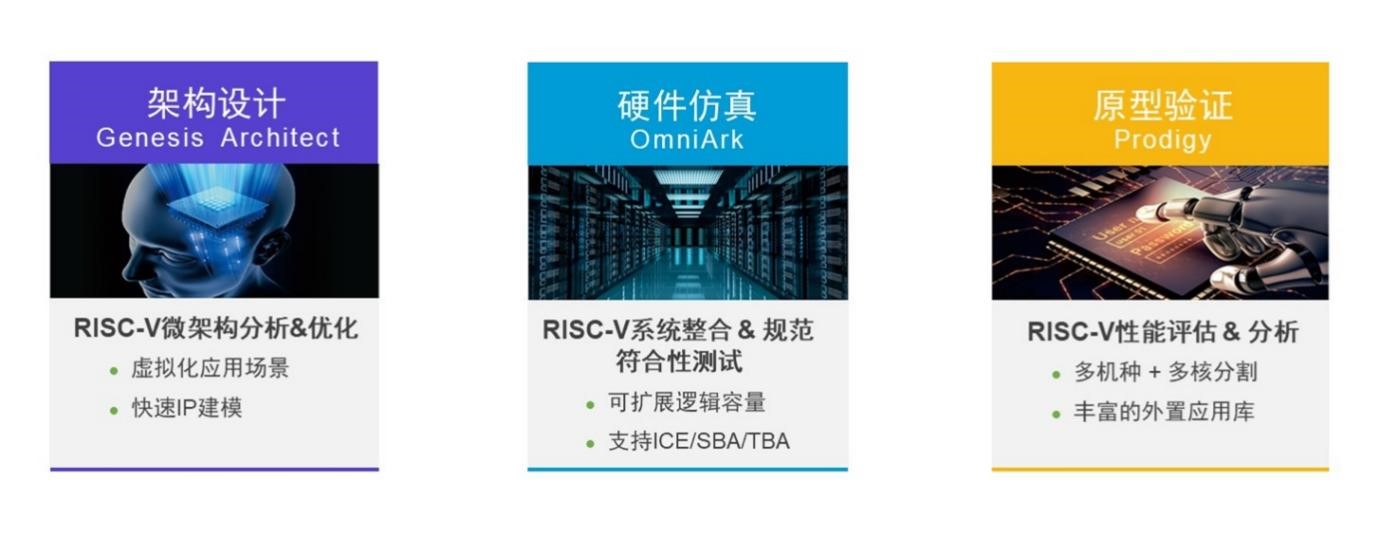

面临这一系列多层次的问题,思尔芯一系列数字前端设计解决方案可以打造一个更高效、稳定的RISC-V平台。针对RISC-V,思尔芯的 “芯神匠”可提供微架构分析和优化,“芯神鼎”可提供系统的全面整合与验证,而“芯神瞳”可提供软件性能评估与分析

“芯神匠”RISC-V微架构建模:

芯神匠提供了一个建模、分析、仿真和软硬件协作的平台,利用建模方法学实现电子系统级(Electronic System Level,ESL)设计流程,可用于开发半导体、航空和汽车电子系统设计产品。通过芯神匠可以进行RSIC-V微架构建模。芯神匠能模拟现有市场上处理器内核的微架构行为,并允许用户在微架构级别添加自定义逻辑。用户可以轻易地调整参数以测试不同配置。例如:芯神匠支持混合处理器(Hybrid Processor)作为IP模块进行模拟,以反映市场上处理器内核的多样性

“芯神鼎”RISC-V系统的全面整合与验证:

芯神鼎是思尔芯自主研发的企业级硬件仿真系统,具备超大规模可扩展阵列架构,设计容量高达20亿门。该系统支持多种仿真验证模式,如TBA和ICE,同时提供信号全可视功能。它特别针对RISC-V系统的全面整合与验证展现出强大的能力。我们正在与第三方合作深入讨论,以制定相应的规范性测试来避免系统碎片化的问题,并提供更多解决方案,例如系统一致性(System coherency)、多核并行处理(Multicore execution)、深度SoC性能分析(SoC profiling)等

“芯神瞳”RISC-V性能分析:

原型验证不仅满足了硬件验证需求,还为芯片开发者构建了在真实硬件上测试软件功能与性能的平台。软件工程师可在此环境下直接开发和调试,显著加速协同开发进程。考虑到RISC-V的多种选择,芯片开发者需对不同供应商和配置的RISC-V核心进行评估,从而选择最适合的方案。思尔芯的原型验证系统能够协助进行SPEC跑分、IO验证以及bsp驱动开发等工作,覆盖了从硬件设计到软件集成的全生命周期。以北京开源芯片研究院(开芯院)旗下的RISC-V处理器“香山”为例。基于思尔芯的芯神瞳VU19P原型验证系统,香山团队运行了SPEC基准测试,通过结合显卡运行Linux和图形界面,以直观地评估其性能。这为团队提供了宝贵的反馈,可以据此进行优化以达到或超过预期的性能标准。目前,第二代“香山”(南湖架构)的SPEC2006得分为20分,性能超越了2018年的ARM Cortex-A76

RISC-V技术已深入到各个领域,其开源、简洁以及高度可扩展的特性正在重新定义计算的未来。核心指令集的开源特性为芯片设计公司提供了保证供应链自主可控的可能性。同时,这种共建共享的机制也促进了RISC-V架构的快速更新和迭代。其多样性既是机会也是挑战。思尔芯针对RISC-V微架构分析,系统整合与规范符合性测试,以及提供软件性能评估提供了多种优化方案。期望能帮助各方更好地整合资源,扩大RISC-V社区,共推新生态发展