加速虚拟原型样机开发,RTL验证和SoC软件验证

基于FPGA的原型系统在运行速度和准确度上都接近流片回来的芯片,所以对于芯片完整的功能性确认以及早期软件开发来说均具有重要意义。但是需要具备丰富的专业知识、大量资源来构建额外的硬件环境、以及互联技术方案,才能构建一个符合标准的原型验证系统。

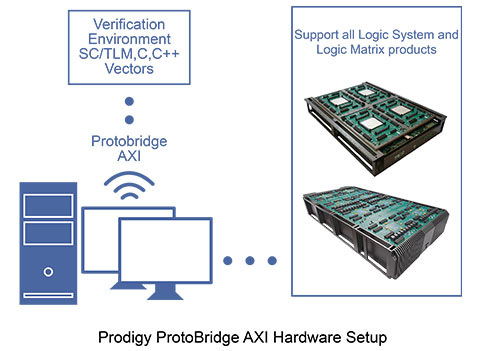

芯神瞳协同仿真软件ProtoBridge通过采用业内广泛使用的 AXI-4 总线协议以及独有的专利技术*,实现了将设计链接到 FPGA 原型验证环境。它建立了一个高吞吐量的数据通道,允许大量的事务级数据在 FPGA 与 PC 主机之间进行交互。

产品特征

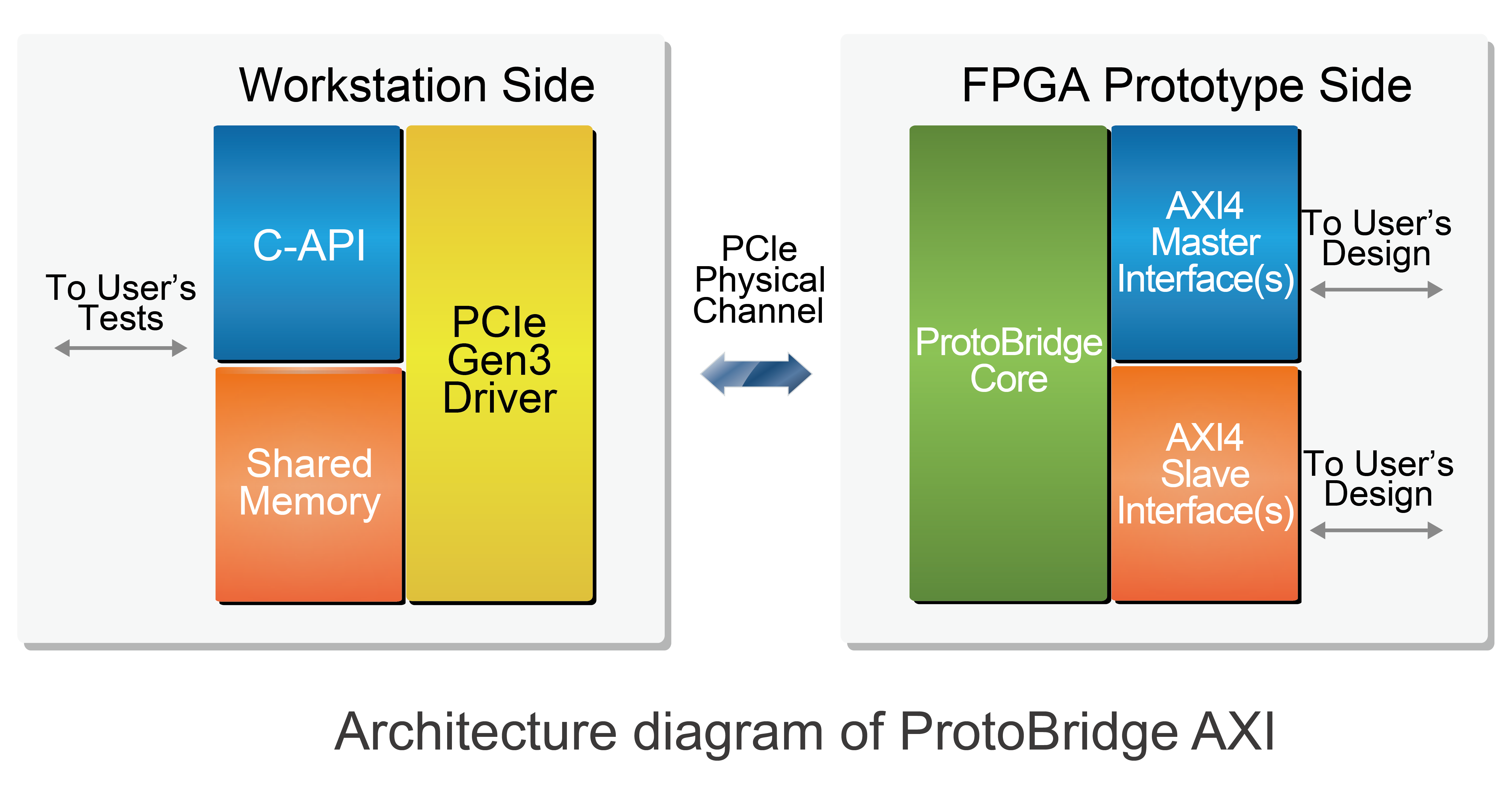

用来进行 FPGA 集成的 AXI-4 事务级互连模块主从接口

在计算机上的一组用来执行 AXI 总线功能的 C-API 函数

针对 Linux 或者 Windows 系统的 PCIe Gen3 驱动程序

包含 FPGA 内部存储演示的参考设计

系统集成指南和详细的产品规格

* 专利号:ZL201911239764.5

在没有完整的 SoC 设计的条件下进行早期的 IP 验证

IP 模块连接到 AXI 总线,可在没有处理器内核和外设的条件下验证

利用 FPGA 原型验证环境在速度性能上的优势,进行早期的算法或架构探究

通过高吞吐量的数据通道缩短验证周期

利用事务级的验证以确保系统结果的准确性

运用 C 代码编写测试激励以减少创建 RTL 测试激励所需的时间和精力

利用测试覆盖率的提升,优化产品的可靠性

利用软件创建边缘测试案例并在 FPGA 原型上测试

使用存储在主机上的测试向量对 FPGA 原型进行高性能回归测试

无需额外的构建特定硬件和软件,进而消除对资源及专门知识的限制

芯神瞳协同仿真软件 ProtoBridge 适用于任何设计,因而可重复使用于多个项目

获得世界领先的支持,准确及时地帮设计团队解决问题,让客户专注于自己的设计本身

FPGA 端口上实例化了 AXI-4, AXI4-Lite, AXI-3 和 AHB 总线连接

可配置的数据位宽,从 32 位到 1024 位

每个主/从实例支持独立的时钟

8 通道的 PCIe Gen3 作为 PC 主机和 FPGA 之间的数据传输通道

大量的数据在 PC 主机和 FPGA 之间传输的速率高达 4000MB/s

支持直接访问和 DMA 访问模式

系统初始化函数调用以实现验证工具环境的管理

中断控制函数调用来标识中断信号源,进而触发 C-API 的后续动作

数据读/写函数调用,与 FPGA 电路进行数据交互

DMA 传输函数调用来执行大量数据的 DMA 操作

利用 PC 内存来存储数据,以减轻待测试设计对存储容量的需求

允许 DUT 与 PC 主机的内存进行数据交互

减少了 DUT 搬移中间数据的次数,进而简化了后续的设计和调试流程

在 PC 同时进行其他任务的情况下,提供了方便的内存访问功能

通过标准的基于 AXI 的 C-API 功能函数与其他的商业或者私有的验证工具兼容

KU115/VU440 Logic Module

VUS/VU19P/VU9P/S10S/S10M Logic System

64 位 Windows 7 系统

64 位 Linux RHEL 6 系统

64 位 Ubuntu 14.04.2 系统

x8 PCIe Gen3