2024年8月21-23日,思尔芯亮相第四届RISC-V中国峰会,与全球RISC-V生态伙伴共同探讨了AI时代RISC-V架构的未来发展。

峰会期间,由于近期思尔芯在架构设计软件的研发上取得了进展,该项目的成员——产品经理梁琪与研发工程师被邀请至演讲台,他们为与会者带来了题为《基于 RISC-V 的架构建模及混合仿真验证方法》的技术演讲。面对当前计算架构日新月异的变革,梁琪深刻剖析道:“RISC-V凭借其简洁的指令集架构,在开源处理器中脱颖而出,前景非常广阔。同时随着多个领域的深入应用,要发展其潜力和优势也将面临很多挑战。”

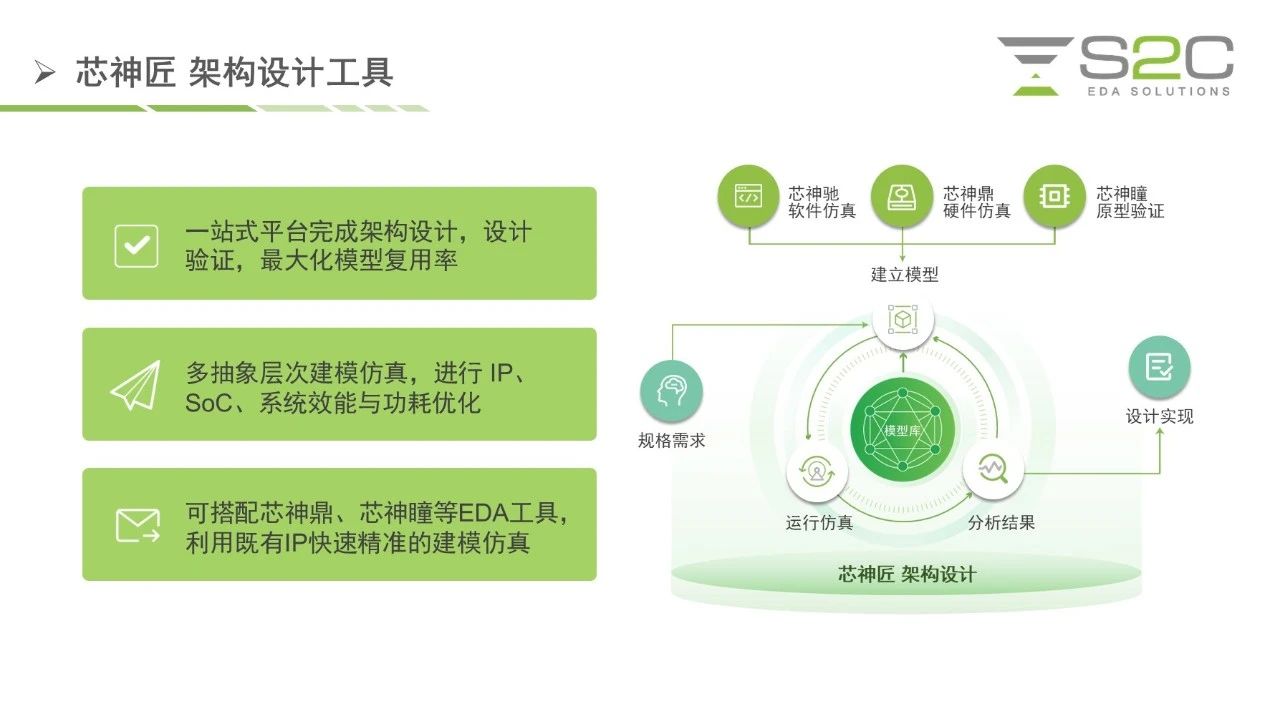

梁琪详细介绍了思尔芯的“芯神匠”架构设计工具,该平台能够一站式完成架构设计、设计验证,并通过不同抽象层次的建模仿真优化IP、SoC及系统。同时可搭配芯神鼎、芯神瞳、芯神驰等EDA工具进行混合仿真。

针对混合仿真技术,梁琪进一步阐述了其重要性及应用场景,包括系统组件间的协同仿真、不同抽象层级模型的结果对比验证等。她强调,混合仿真技术对于提升设计验证效率与关键部件的验证是一种重要的手段。

随后,由开发这一EDA工具的工程师深入剖析了混合仿真技术在架构设计中的技术逻辑。他表示,思尔芯的混合仿真框架不仅基于图形化的架构建模方式,提供了直观易用的操作界面,还通过紧密结合架构建模与混合仿真验证,实现了对设计错误的快速发现与精确定位,极大地提升了设计效率与质量。

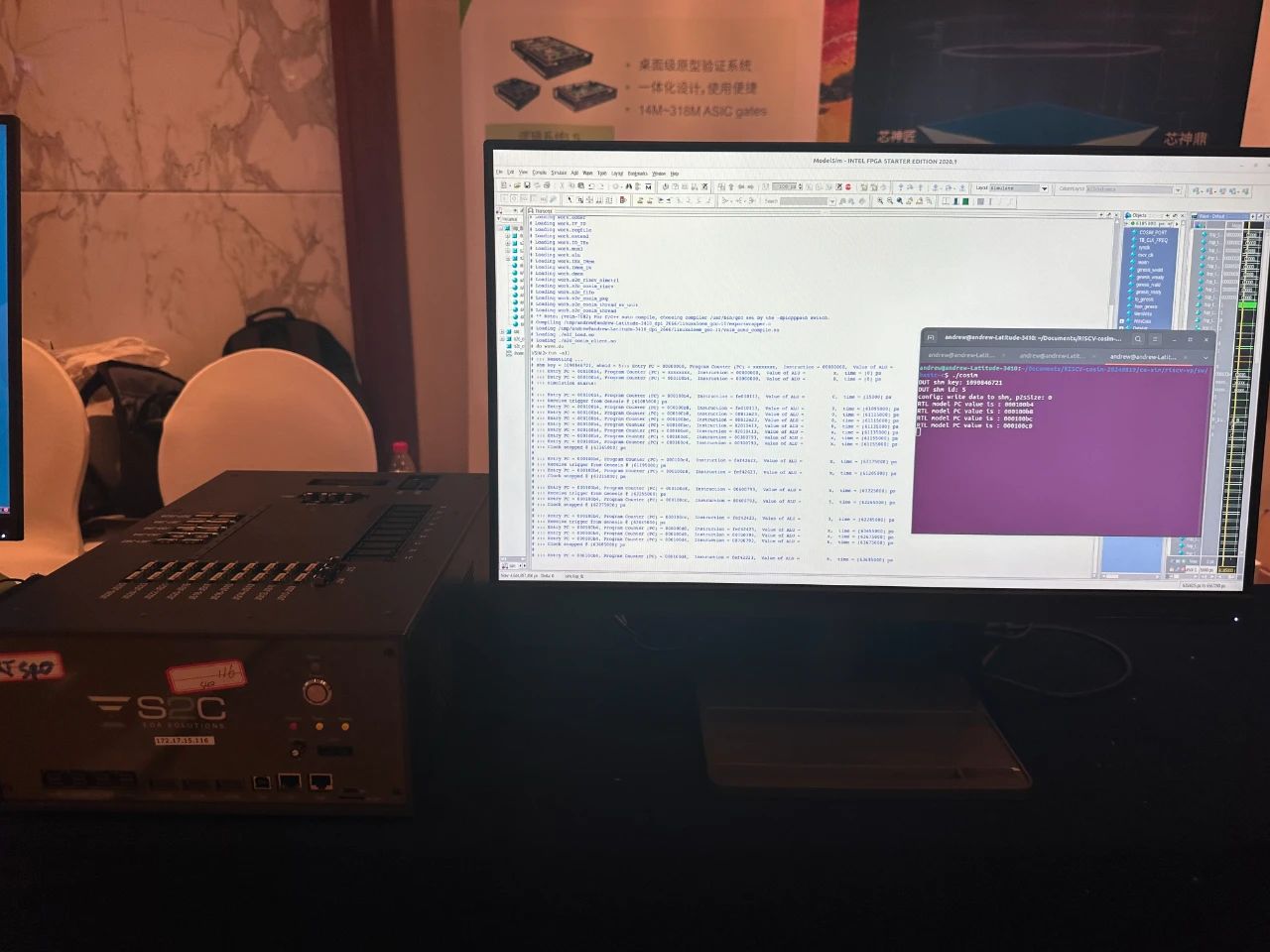

展会现场,思尔芯更是以一系列硬核产品惊艳亮相,通过生动的现场Demo体验,向与会者全方位展示了其在RISC-V领域的技术实力与创新成果。其中,RISC-V香山图形化显示项目作为RISC-V架构芯片设计的先锋之作,不仅彰显了思尔芯在原型验证技术方面的独特优势,更为RISC-V架构的广泛应用树立了新的标杆。此外,演讲中提及的架构设计与软件仿真的实际运行Demo,同样吸引了众多与会者的目光,成为展会上一大亮点。

此次RISC-V中国峰会的成功举办,不仅为RISC-V生态的繁荣发展注入了新的活力,也为思尔芯等优秀企业提供了展示自我、交流合作的宝贵平台。展望未来,思尔芯将继续秉承创新精神,携手全球生态伙伴,共同推动RISC-V架构在AI时代的蓬勃发展,开启计算架构的新篇章。

更多资讯,请点击:www.s2ceda.com