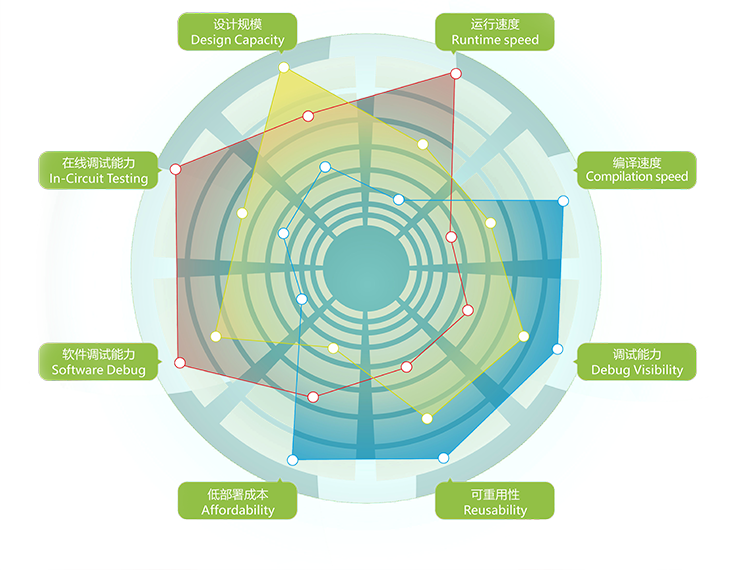

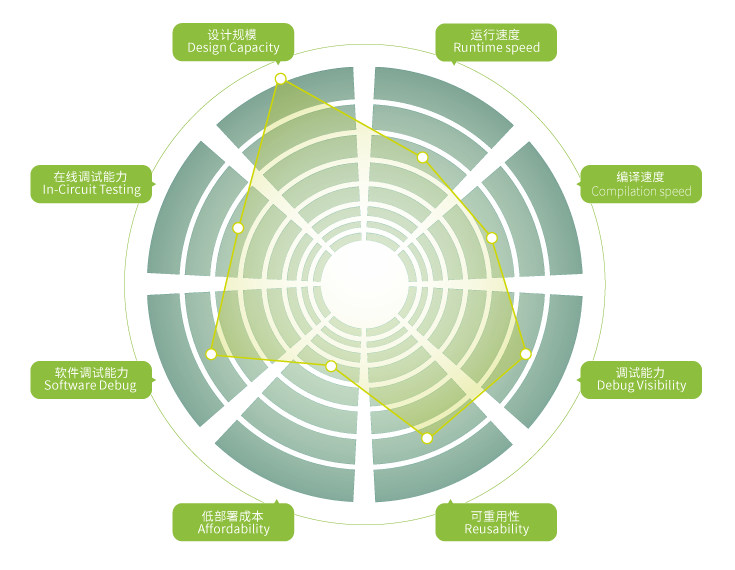

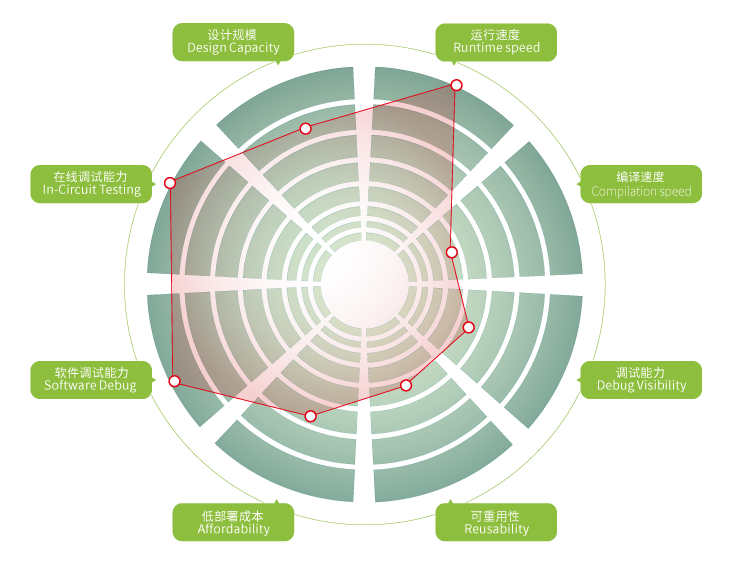

SOC/ASIC 设计规模不断增大,且结构愈加复杂,导致验证的复杂度呈指数级增长。为了缩短芯片的上市周期,在不同设计阶段选择不同的验证工具,提高生产效率,加速验证的收敛显得尤为重要。考量设计规模,在线调试能力,软件调试能力,低部署成本,可重用性,调试能力,编译速度和运行速度,选择不同的验证工具,完成日益复杂的验证项目。

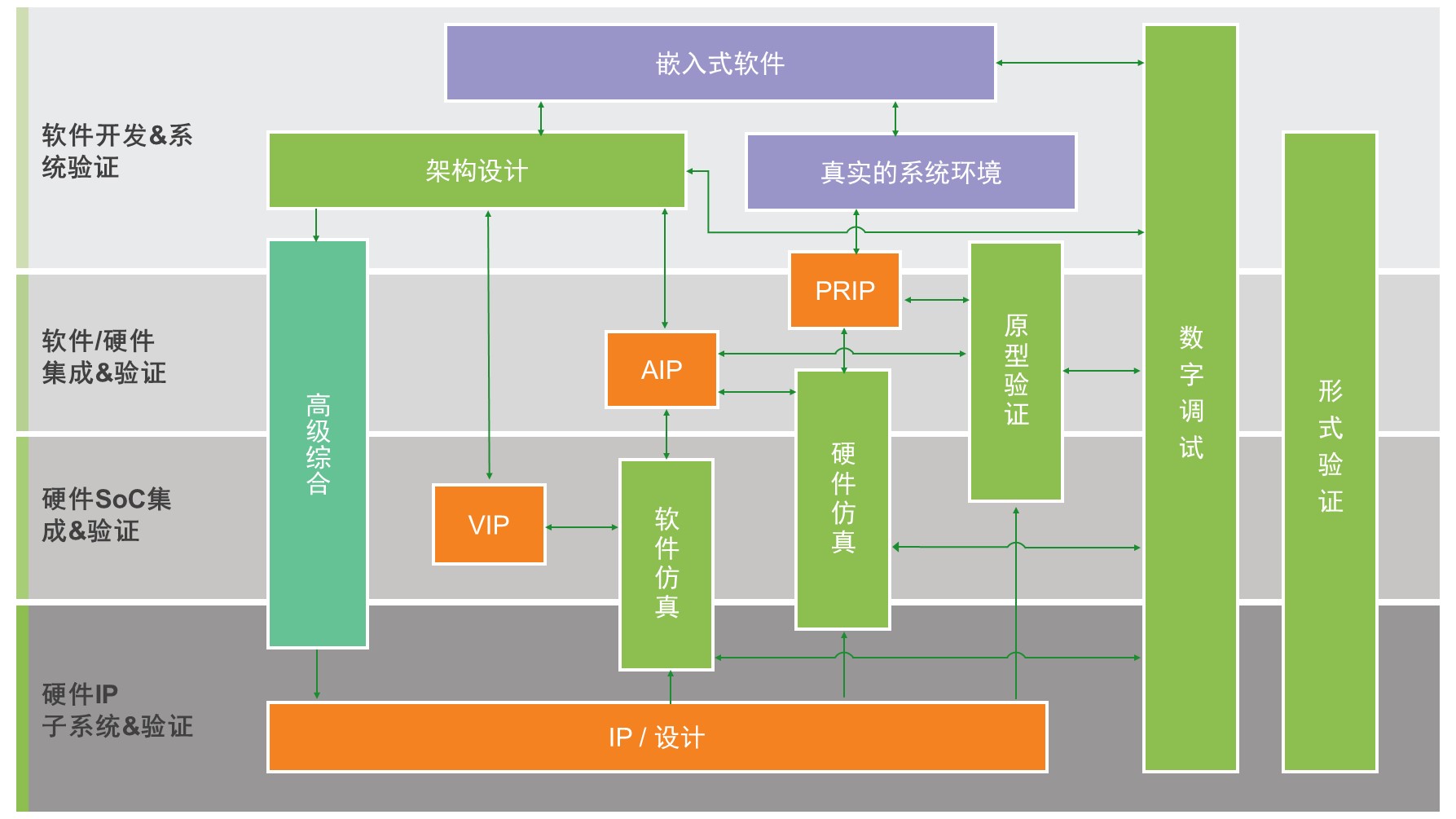

在芯片开发的各个阶段会有不同的设计与验证需求,我们的多个产品组合可满足从 IP 开发、SoC 集成、软硬件集成、软件开发、系统验证等各阶段的设计验证需求。通过使用我们的通用数字电路调试软件和丰富的验证 IP 库,建立统一的设计、验证与调试环境,确保在同一芯片项目开发中, 不同团队能够实现高效协作,从而提高整体开发效率。