在人工智能(AI)技术蓬勃发展的今天,芯片的复杂度正以前所未有的速度飙升,轻松跨越了百亿逻辑门级别的大关。这一趋势不仅推动了半导体行业的快速发展,也对硬件仿真系统提出了更高的挑战和要求。在近日的ICCAD-Expo 2024上,思尔芯研发总监余勇发表了精彩技术演讲,他深入探讨了AI时代下高性能硬件仿真系统的重要性。他指出:“随着AI技术的广泛应用,芯片的复杂度急剧增加,传统硬件仿真的系统运行性能已难以满足当前的设计需求。因此,思尔芯迭代升级了其OmniArk芯神鼎国产硬件仿真系统,该系统支持从2亿到96亿门的灵活配置,系统运行性能高达4-6MHz,能够满足复杂芯片设计的仿真需求。”

新一代芯神鼎硬件仿真系统凭借其卓越的性能和丰富的功能,广泛应用于系统架构探索、硬件调试、软件开发、全系统验证以及软硬件协同等多个领域。

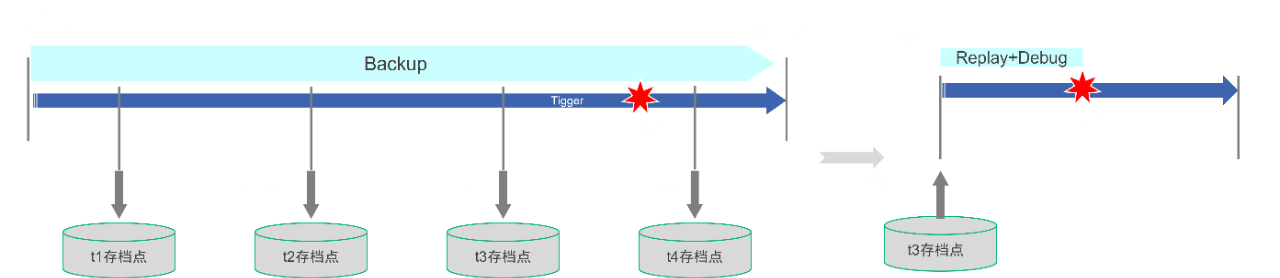

1 随机性问题调试——Backup/Replay的神奇力量

2 从指定仿真时间点恢复调试——Save/Restore的便捷之处

写在最后

思尔芯S8-100单核等效逻辑门约1亿门,相较于前代逻辑系统S7-19P,其容量提升了2倍。此外,S8-100的I/O带宽也提升2.5倍,并配备了更灵活、可扩展的I/O架构,轻松应对不同外设与复杂互联拓扑的需求。S8-100透过GTYP支持PCIe Gen5,并提供8个速率高达56Gbps GTM的MCIO接口,带来强大性能和高效体验。以RISC-V应用领域为例,单核S8-100系统就能满足较大RISC-V核的验证,即便是复杂的RISC-V核也无需分割,从而提升高达3-5倍运行频率,使得软件工程师开发更加得心应手。对于AI和HPC等领域的大规模设计,容量的翻倍使得分割数量大幅度减少,显著降低了拓扑结构的复杂性,工程师们能够更加轻松地组网与优化。

此外,思尔芯还提供丰富的外置应用库,包含多种外设接口子卡、降速桥、内存模型等,并且可提供验证就绪的参考设计,简化用户验证环境的部署。为了满足主流应用领域的需求,思尔芯还提供多种灵活的接口方案包括丰富的高速接口降速桥和内存接口转换IP,例如PCIe Gen5 、400G以太网、LPDDR5/DDR5等。S8-100还支持多核FPGA的深度调试,进一步提高了系统部署的速度和效率。

面对不断变化的AI大模型应用场景,思尔芯推出的芯神瞳逻辑系统S8-100全系列,基于公司20余年的技术积累和不断迭代。自成立以来,思尔芯已发布了8代原型验证系统,这些成熟易用的产品经过市场验证,已广泛应用于全球600多家企业。思尔芯始终秉持“以客户为中心、快速响应”的核心价值,产品覆盖从架构设计、软件仿真、硬件仿真到原型验证、数字调试、EDA云等全方位工具和服务,通过完善的数字前端EDA解决方案,为客户提供高效、可靠的支持,助力加速芯片设计创新。

欲了解更多信息,请点击:https://www.s2ceda.com/ch/product-prototyping-ls-465