作者: 沈丛 | 来源:中国电子报、电子信息产业网

近日,思尔芯推出了一款企业级硬件仿真系统 OmniArk 芯神鼎,该款产品采用了超大规模可扩展商用阵列架构设计,最大设计规模可达 20 亿门,满足从 IP 级到系统级的功能验证。此外,该款产品还具备全自动编译流程、高效调试纠错能力、丰富的仿真验证模式,以及千倍以上的仿真加速。

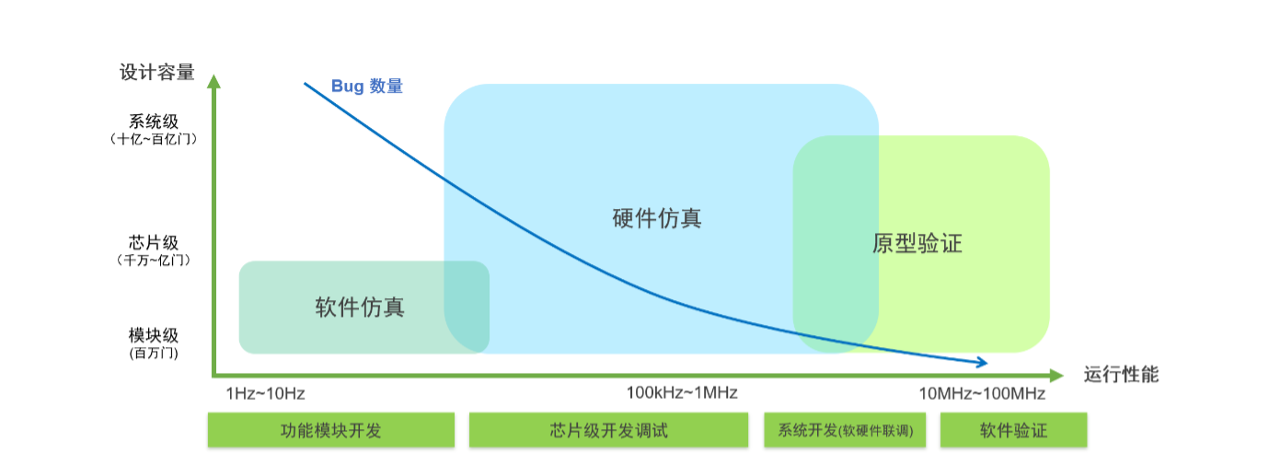

据思尔芯 CEO 林俊雄介绍,在数字电路设计中,设计和验证团队通常采用软件仿真、硬件仿真及原型验证三种验证工具,三种方式各自具备不同的优势且优势互补。但是硬件仿真作为软件仿真和原型验证仿真的承接点,愈发受到市场的关注,且已经成为数字电路设计中的焦点技术之一。

据林俊雄介绍,在三种验证工具中,软件仿真验证工具最易于使用,不仅成本效益高,还具有复杂的调试能力。但在大规模数字电路设计中,其劣势也开始逐渐显现出来。这是由于设计的结构越复杂,仿真所需要的时间就越长,软件仿真的效益会受到限制,在对高级语言进行编译分析的过程中,依旧需要通过硬件仿真来完成。

原型验证通常只用于芯片设计的前端流程,能够模拟芯片的功能和应用环境,以此来验证芯片的整体功能,并提供片上的软件开发环境,相比硬件仿真,原型验证的运行速度更接近于真实芯片,可以配合软件开发者来进行底层软件的开发。但原型验证平台则缺乏调试的灵活性,因此常常用于流片之前的系统集成与软件调试。

因此,硬件仿真验证作为软件仿真原型验证的桥梁,即具备设计容量大、可扩展性好的优势,还具备仿真速度快、调试能力强、调试模式多样等优势,适合大型设计从模块级、芯片级到系统级的仿真验证。“近年来,由于大数据处理及AI芯片设计规模的不断扩大,市场竞争也愈发激烈,对于芯片设计的迭代需求也越来越大,因此,越来越多的芯片设计公司考虑选择硬件仿真系统,来提高芯片验证效率,缩短芯片开发周期。”林俊雄说。