TAKUMI 公司成立于 2003 年,授权为嵌入式系统和移动信息装置包括数字照相机/摄像机,移动电话和机顶盒提供其独特的 OpenGL ES- 和 OpenVG- 兼容图形加速器 IP 核,可最小化尺寸和能量功耗以及真正丰富全世界 2D/3D 直观用户的界面。公司总部位于东京 Shiba,并在山梨甲府设有办事处。

当今的图形 IP 非常复杂,需要大量的测试模式才能执行完整的硬件验证和软件测试。 因此,需要一个可靠,灵活且高性能的 FPGA 平台。此外,计划集成复杂 IP 核(例如 TAKUMI 的 3D 图形 IP )的 SoC 设计人员通常需要大量的验证工作,例如验证所有硬件功能的正确性,评估 SoC 总线效率和测试软件兼容性。因此,拥有一个易于使用且可扩展的基于 FPGA 的快速原型开发平台,并已在该平台上验证了TAKUMI 的 3D 图形 IP 内核,无疑会简化最终 SoC 的集成。

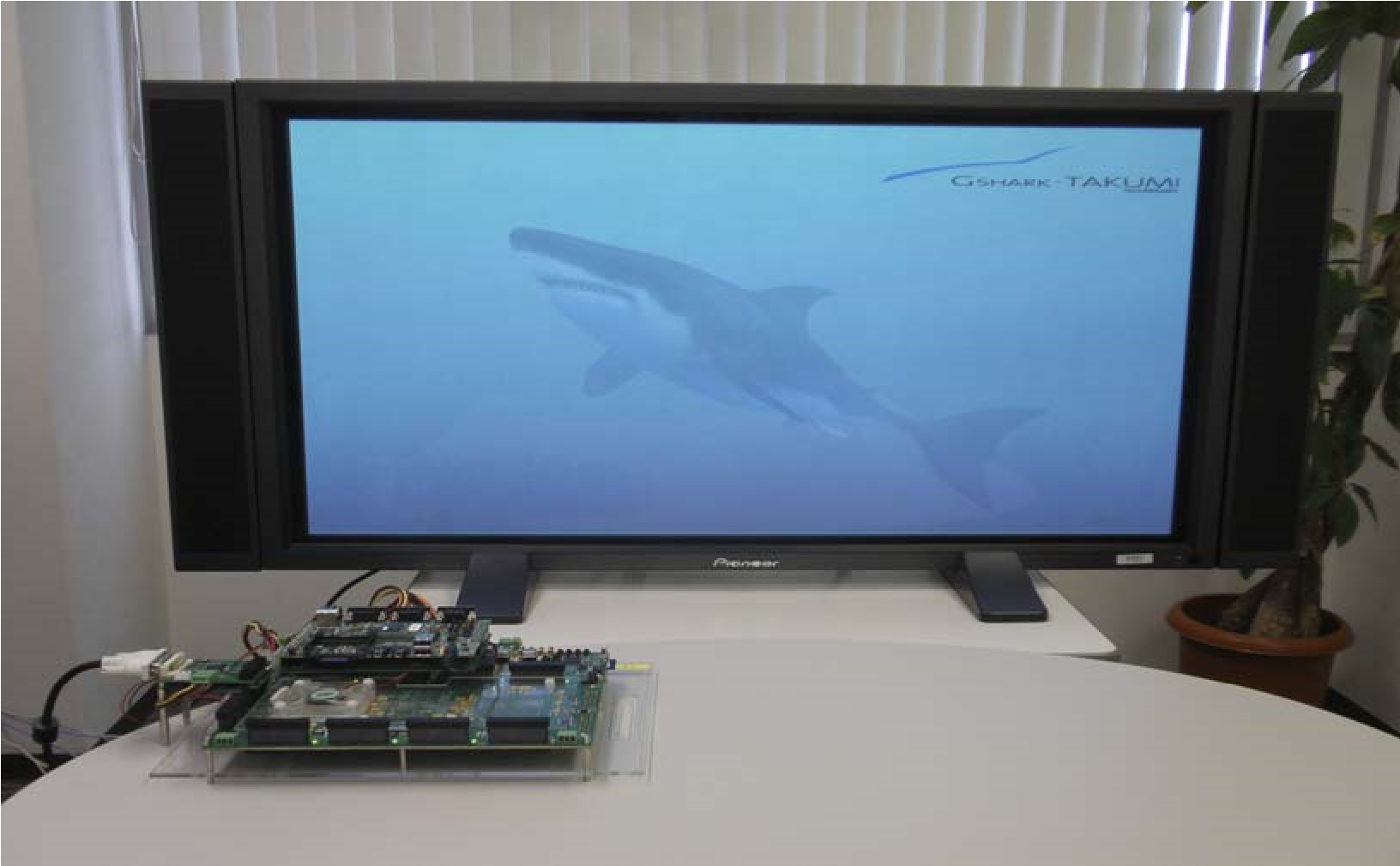

将 3D 图形 IP 内核映射到了 Virtex-6 760 S2C 的 V6 TAI 逻辑模块上的 FPGA,并使用 S2C 的 DVI-ver2.0 子卡在电视上显示视频。TAKUMI使用 S2C 的 Virtex-6 760 Prodigy 逻辑模块为一系列图形 IP 内核(包括 GS3000 和 GSV3000 内核)高速运行各种测试模式。这些 TAKUMI IP 内核已经在 FPGA 中进行了全面验证,可以轻松地向 TAKUMI 客户演示和评估。从而大大减少了片上系统(SoC)集成时间。为了控制图形 IP 内核,使用了现成的 ARM11 CPU 板(ARMADILLO-500)和 S2C 在日本的合作伙伴 Japan Circuit 定制接口板,以便可以将 ARM11 CPU 板插入S2C 的 V6 TAI Logic 之上。

S2C 的快速 SoC 原型解决方案以其可靠性,针对各种 SoC 模型和接口的接口灵活性以及可支持各种门数设计的可扩展性而闻名

大容量和高稳定性使 TAKUMI 能够高速运行所有不同的测试模式

S2C 支持团队的快速响应帮助 TAKUMI 成功地建立了他们的 FPGA 验证环境

利用 S2C 的快速 SoC 原型解决方案,TAKUMI 的 Graphics IP 核被原型化,并已作为参考设计提供给 S2C的 Virtex-6 760 TAI 逻辑模块,供客户集成到他们的 SoC 中。 TAKUMI Graphics IP 内核参考设计还可以根据客户要求轻松移植到新的 Virtex-7 2000T TAI 逻辑模块系列或 Altera Stratix-4 820 TAI 逻辑模块系列。